论文总字数:43068字

摘 要

时分复用(TDMA)数字基带通信系统广泛应用于各种数字通信场合,以实现信道的复用,有效地传送数字信息。对于TDMA系统的设计,工程上已有许多现成的电路及芯片可采用,其设计关键包括位同步信号,帧同步信号的产生、码型变换及反变换、防抖动等。

Xilinx公司的Platform Studio提供了一个通用的完全集成的硬件/软件开发环境,支持所有Xilinx处理器解决方案。这样的嵌入式系统可以将FPGA硬件语言在数据计算上快速高效的优势和Microblaze软核运行速度快、占用资源少、可配置性强等优势有效结合起来,构建更可靠高效的嵌入式系统。

在时分复用过程中,系统可以根据用户需求动态分配各路数据复用所占时隙大小,这样的分配方式虽然在一定程度上增加了系统的复杂度,但可以更加高效的进行数据传输工作,具有很好的应用性和可行性。

关键词:Microblaze;时分复用;VHDL;IP模块;时隙可变。

THe REALIZATION OF DIGITAL COMMUNICATION SYSTEM BASED ON TIME-DIVISION MULTIPLEXING WITH XILINX CPU MICROBLAZE

Abstract

Baseband digital communication system based on Time-division multiplexing (TDMA) is widely applied in all kinds of digital communication occasions, in order to realize the channel multiplexing and to transmit digital information effectively. For the design of a TDMA system, there are many ready-made circuits and chips. The keys of a TDMA system include sync signal generation, vertical sync signal generation, transformation of codes, its inverse transformation, shake and so on.

Platform Studio, a software which is produced by Xilinx Company, provides a general fully integrated hardware/software development environment. It supports all kinds of Xilinx processors. Such embedded systems can combine the advatages of FPGA, whose hardware language can work fast on the area of data calculation, and the advantage of Microblaze Soft-Core, which has high running speed, less resource-intensity, strong configurability. This kind of combination can build a more reliable and efficient embedded system.

In the process of time division multiplexing, the system can allocate the size of time slots, which are used for different signals, dynamically according to the requirements of users’ data. Athough this improvement inreases the complexity of the system to some extent, it can be more efficient for data transmission. So this technology has good feasibility and applicability.

KEYWORDS: Microblaze, TDMA, VHDL, IP Module, Available Time Slot.

目录

用Xilinx的嵌入式CPU Microblaze实现多种通信业务复用及解复用 I

摘 要 I

Abstract II

第1章 绪论 5

1.1 引言 5

1.2 通信TDM时分复用解复用原理 5

1.3 Xilinx Microblaze原理及EDK开发流程 6

1.3.1 MicroBlaze处理器结构 6

1.3.2 EDK工具开发流程 7

1.4 本文的研究目的和主要研究内容 8

1.4.1 时分复用通信及时隙可调技术实现 8

1.4.2 Microblaze软核与传统FPGA硬件平台的结合 8

第2章 Microblaze总线系统搭建 10

2.1 总线系统需求 10

2.2 Microblaze平台设定 11

第3章 复用解复用业务的原理及实现 15

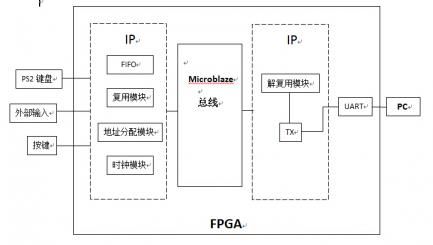

3.1 系统硬件框架 15

3.2 系统软件流程 16

3.3 硬件核心部分的设计 16

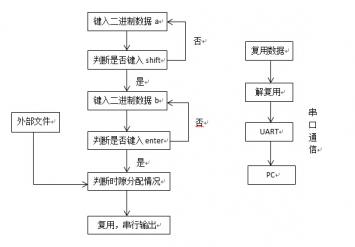

3.4 复用解复用算法实现 16

3.4.1 多路信号复用的模型 16

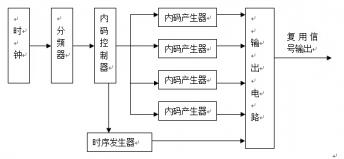

3.4.2 分频器模块设计 17

3.4.3 内码控制器模块设计 18

3.4.4 数据选通控制器模块设计 19

3.4.5 四路信号复用模块设计 20

3.5 解复用算法及实现 23

3.6 PS2键盘模块设计 23

3.6.1 PS2接口物理特性 23

3.6.2 PS2接口协议原理 23

3.6.3 PS2主设备到从设备的通信 24

3.7 FPGA与PC通讯 31

3.7.1 通信方式的选择 31

3.7.2 UART通信协议及实现 32

3.7.2.1 通信协议 32

3.7.2.2 UART工作原理 33

3.7.2.3 UART通信协议实现 34

第4章 系统功能仿真及验证 41

4.1 硬件部分设计参数 41

4.2 分频器模块仿真图 45

4.3 内码产生器模块仿真图 45

4.4 数据选通控制器模块仿真图 45

4.5 四路信号复用模块仿真图 46

4.6 UART通信模块仿真图 46

4.7 系统四路信号复用解复用仿真图 47

4.8 结论 47

参考文献 49

致谢 50

绪论

引言

在基带通信系统中,时分复用技术广泛使用在各种各样数字通信的设备中,用来完成多个信道上数据的复用,在两个系统间传送数字数据信息。针对于时分复用系统的设计,已经有许多现成的电路和芯片被应用在各种工程中,其设计的重点涉及位同步信号,帧同步信号的生成、码型变换、反变换、防抖动等方面。

在众多电子设计技术领域,大规模可编程逻辑器件FPGA的广泛使用,为诸多领域的数字系统的设计和制作带来很大的灵活性和自主性。因为FPGA平台可以通过软件编程的方式对自身硬件的结构和工作方式进行重新设定,所以让硬件平台的设计可以像软件设计那样方便快捷。同时,也是基于这样优越的EDA技术使用背景.本文采用VHDL硬件编程语言,成功地对时分复用数字通信系统的主要关键硬件电路进行逻辑描述和程序仿真,模块包括信号变换、位同步和帧同步信号、信号终端等,同时使用Xilinx的嵌入式软核Microblaze构建AXI4系统总线控制系统工作,通过EDA软件ISE成功地将系统的代码下载到FPGA芯片上。由于系统硬件的高度集成化,确保系统整体性能稳定,抗干扰能力也大大增强。

通信TDM时分复用解复用原理

时分复用多址技术TDMA(Time Division Multiple Access)是将时间周期性地划分为帧的形式,每一帧再由若干个时隙组成,每一个时隙是一个TDMA信道,系统通过判断用户使用情况,将时隙动态分配给各个信道。

设计人员依据系统时隙分配的准则,控制每个发送点能够在规定的各个时隙中进行数据的收发,同时因为时钟同步的原则和帧结构相同的准则的约束下,各个发送接收设备能够在每个时隙内同时接收外部传输过来的信号,并且同一地点的不同设备并不会互相干扰。基于设定好的时隙分配和同步时钟,只要同一个传输系统能够保证每个数据发送点都在固定时隙进行数据接受过程,则必然可以在复用信号中成功解复用出各分路信息。

TDMA时分复用通信系统的特点如下:

由于TDM通信协议实现较为简单,通信系统中的每个发送接收点可以只使用一个发射机,因此在一定程度上可以减弱因不同工作频率的不同设备同时进行数据收发二产生的干扰问题。

频率规划简单。TDM通信系统采用分割时隙的设计方式,并不涉及类似于频分复用中频段上进行划分的问题,因此在设备需要上的要求不高,同时也更加容易进行不同信道的动态分配。

TDM通信系统可以在每个帧结构的其他空虚时隙中,设计人员可以编写相关的算法来检测传输和接收到的数字信号的强度和其他相关信息。设计人员可以通过这些信息来加强和控制其通信系统,使其更稳定可靠地工作,同时通过设计人员对相关参数的控制和改变也可以在系统各个数据发送点进行越区切换工作,提高系统工作效率。

TDM通信系统正常工作的前提是要保证不同发送点不能在数据接收过程中产生数据的重叠等错误,所以必须完成不同设备间的时钟同步任务。与此同时该任务也是TDM技术在真正应用到日常生活中的主要技术困难,现在已有较为成熟的解决方式,但还需要不断的研究和改善,提高系统整体稳定性。

Xilinx Microblaze原理及EDK开发流程

MicroBlaze处理器结构

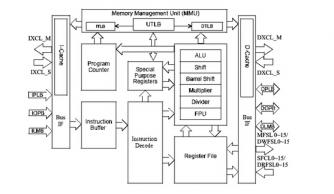

在Microblaze的指令集体系结构中,MicroBlaze的结构非常类似于流行的计算机体系结构,即Patterson描述的基于RISC的DLX架构。除了少数指令例外,MicroBlaze发出的新指令,在大多数情况下能在每个周期内保持单周期吞吐量。

MicroBlaze具有多功能的互连系统,以支持各种嵌入式应用。MicroBlaze可以设定的I/O总线方式中包括CoreConnect PLB总线,能与主/从功能的传统系统内存映射事务总线。新版本的MicroBlaze可以使用在Spartan-6和Virtex-6以及7系列,同时支持AXI4协议规范。多数供应商提供Microblaze和第三方IP接口。对于访问本地存储器(FPGA BRAM),MicroBlaze使用专用LMB总线,从而减少系统总线上的数据负担。用户定义的协同处理器通过名为FSL(快速单链路)的专用FIFO风格的进行连接。协同处理器的多个接口可以通过卸载或计算至用户设计的硬件模块进行整体加速设计。

MicroBlaze的许多方面都可以由用户设置:缓存大小,通道深度(3级或5级),嵌入式外设,内存管理单元和可定制总线接口。面积优化版本的MicroBlaze采用了3级流水线,通过牺牲时钟频率的方式来降低占用的逻辑区域。性能优化的版本扩展执行管线可以设定为5个阶段,从而允许210兆赫的最高速度(Virtex-5 FPGA系列)。另外可以选择性地添加/删除键处理器指令(即乘法,除法和浮点运算)。这种定制使开发人员能够做出相应的设计权衡一组特定的主机硬件和应用软件的要求。

在存储器管理单元方面,MicroBlaze能够承载需要基于硬件的寻呼和保护的系统,如Linux内核的操作系统。否则它仅限于具有简化保护和虚拟存储器模型的操作系统,例如FreeRTOS或Linux(没有MMU的支持)。

嵌入式软核MicroBlaze的诸多特性很大程度上扩展了其应用范围,Xilinx公司一直不断更新MicroBlaze处理器内核的版本和性能,目前我使用的版本是MicroBlaze version7.1,该版本内部架构如图1-1所示。

MicroBlaze处理器结构图

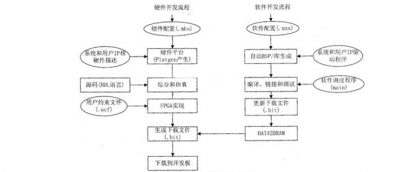

EDK工具开发流程

Xilinx公司的EDK(嵌入式开发套件)的开发包为赛灵思FPGA的MicroBlaze建设(和PowerPC)嵌入式处理器系统。托管在Eclipse IDE中,由两个独立的环境构成:XPS和SDK。

设计师使用XPS(Xilinx平台工作室)来配置和建立自己的嵌入式系统(处理器核心,内存控制器,I / O外设等)的XPS转换设计师的平台规范成可综合RTL描述的硬件规格(Verilog或VHDL),并写了一组脚本来自动嵌入式系统(从RTL到比特流文件)。对于MicroBlaze内核的实现,通常EDK生成一个加密的(非人类可读)网表,但是处理器的说明(写于VHDL)可从赛灵思公司购买。

SDK处理的程序是将在嵌入式系统上执行的软件。搭载了GNU工具链(GNU编译器,GNU调试器),SDK允许程序员编写,编译和调试C / C 应用程序的嵌入式系统。赛灵思包括一个周期精确的指令集仿真器(ISS),给程序员测试在模拟的软件,或用合适的FPGA的板下载和实际系统上执行的选择。

EDK或ISE设计套件嵌入式版(IDS)的购买者被授予永久许可使用的MicroBlaze在赛灵思FPGA与没有经常性使用费。该许可不授予使用MicroBlaze的赛灵思器件,它必须直接与Xilinx协商之外的权利。

替代编译器及开发工具已经提供来自Altium的,但一个EDK安装和许可证仍然需要

剩余内容已隐藏,请支付后下载全文,论文总字数:43068字

相关图片展示: