论文总字数:32940字

目 录

1.绪论 1

1.1研究背景 1

1.2研究意义 1

1.3国内外研究现状 2

2.FPGA概述 2

2.1 FPGA简介 2

2.2 FPGA工作原理 3

2.3开发平台Quartus II概述 3

2.4 Verilog HDL语言概述 4

3.总体方案设计 5

3.1设计目标 5

3.2 系统设计方案 5

4. 系统硬件设计 5

4.1 FPGA最小系统模块 5

4.1.1 系统主芯片 5

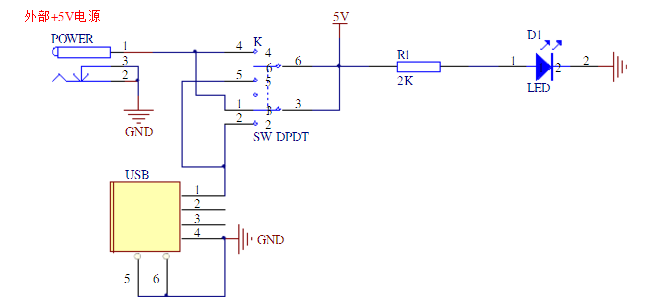

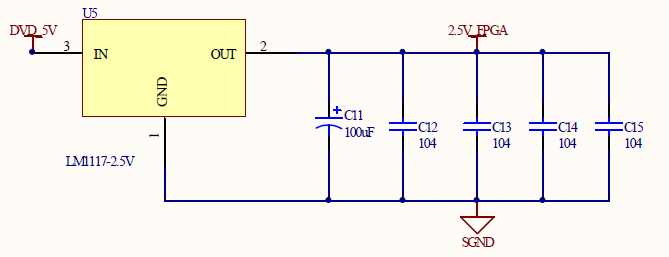

4.1.2电源模块 6

4.1.3时钟信号模块 7

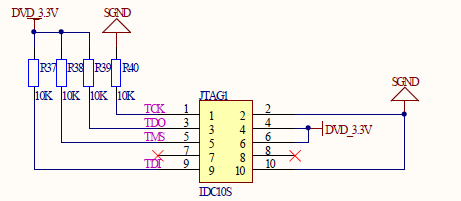

4.1.4调试接口模块 8

4.1.5复位模块 8

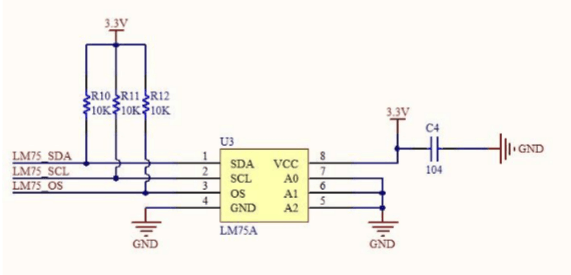

4.2温度测量模块 8

4.3显示模块 10

5. 系统软件设计 11

5.1 软件设计总思路 11

5.2 分频模块 11

5.3综合计时模块的软件设计 12

5.3.1公历闰年计算方法 12

5.3.2综合计时模块设计思路及实现 12

5.4数据调整模块的软件设计 15

5.4.1 数据调整模块的设计思路 15

5.4.2按键消抖的实现 15

5.5温度测量模块的软件设计 16

5.5.1 I2C通信协议 16

5.5.2温度测量模块的设计思路 18

6.系统调试 21

6.1硬件调试 21

6.2软件调试 21

6.3软硬件联调 23

7.总结 25

参考文献 26

致 谢 27

附录 28

基于FPGA的万年历设计

石钰

摘要:万年历在人们的生活中一直扮演着重要的角色,可随着时代的发展,传统的纸质万年历已经越来越无法满足人们对于时间精确度以及便捷性的要求。随着电子科学的不断发展与进步,各式各样的电子万年历也随之出现。本文在Quartus II环境下,运用FPGA芯片开发,Verilog HDL语言编程,来实现一个基于FPGA的电子万年历。选用FPGA来实现电子万年历的优势在于外围电路相对简单、系统的集成化程度高且设计过程也相对灵活,最重要的是在精度方面比之现在市场上的一般电子万年历也有着显著的优势。

关键词:万年历,FPGA,Quartus II,精度

Design of Calendar Based on FPGA

窗体顶端

Abstract: The calendar has played an important role in people's life. With the development of the times, the traditional paper calendar has become increasingly unable to meet people's time precision and convenience requirements. With the continuous development of electronic science and progress, a variety of electronic calendar also appears. In this paper, Quartus II environment, the use of FPGA chip development, Verilog HDL language programming, to achieve a FPGA-based electronic calendar. The advantage of using FPGAs to achieve electronic perpetual calendar is that the external circuit is relatively simple, the system is highly integrated and the design process is relatively flexible. The most important thing is that there are significant advantages in precision than the general electronic calendar in the market today.

Keywords: calendar, FPGA, Quartus II,accuracy

窗体底端

1.绪论

1.1研究背景

在当代快节奏的工作、生活中,时间与我们每个人的联系变得越来越紧密,人们对于时间的重视程度也在不断地提高。随着科学技术的不断发展,人类得知时间的手段也在不断改变,从观察太阳的不同时间所处的位置从而得知、到利用摆钟,再到发明现在的电子钟,一直在不断地创新,不断地进步。而记录日期的方法也从原先的用笔记录,到用纸质万年历记录,再到利用电子万年历记录,这些方法一直在不断地方便着人们的生活[1]。而且为了使人们能清楚的了解当前时间、日期等信息的同时,还可以让人们方便的了解日常生活中的相关信息(如气温、湿度等),电子万年历出现在了市场上。它汇聚了人们平时生活中所需要的各种基本数据,既能让人们快捷地了解到生活所需要的数据,还具有显示数据直接、功能丰富且贴近生活等多种长处。电子设备生活化,也是现在电子产业发展的主流趋势。

现代电子技术发展的越来越快了,电子设计也变得更贴近生活、更在乎用户体验,使得人们的日常生活也发生了根本性的改变。更重要的是电子万年历的出现也使人们的生活变得更加便利,也被广泛的使用在诸多场合,比如住家的客厅,卖东西的商铺、酒店的大堂以及火车站和机场,我们也随处可见电子万年历的身影,不仅方便了自己也方便了他人。不仅在功能上变得越来越丰富,在外形上不是有不断的开发和进步,使的电子万年历具有广泛的市场需求。

1.2研究意义

近年来,科学技术正在迅速地发展以及大面积地普及,同时我们的工作和生活也在发生翻天覆地的变化,随之而来的就是生活和工作观念的改变,这使得人们不断提高对电子产品的要求,同时这也促使了与我们生活有关的电子设备正逐步向更加智能,更加精确,更加便捷的方向发展,万年历正是这类电子设备的代表之一。自古以来,人们就有使用日历的习惯,它既是一种装饰,又能显示日期节气等信息。不过,到了现在,这类纸质日历的弊端变得越来越明显,一旦忘记按时翻页或者撕去一张,可能会错过重要的事情,并且,制造纸质日历需要耗费大量的纸,这一点与我们现代社会可持续发展的理念不吻合。因而电子万年历普遍受到了人们的欢迎,其使用方便,显示直接明了,信息丰富且更加准确等特点更是为人们的日常生活提供了不小的便利。

技术的进步使人们对于电子产品精度的要求逐渐提高,尤其是与时间相关的电子产品的精度。人们对于现有的电子万年历的精度已经越来越不满意,本设计基于FPGA,它最大的特点就是在于精度高,正好可以满足人们对精度的高要求[2],具有良好的市场前景及发展空间。

1.3国内外研究现状

近十年来,国内的电子万年历厂商逐渐开始重视对相关技术的研发与拓展,越来越多的电子万年历出现在生活中的各个场合中,功能也在不断的加强和进步。不过就算是这样,国内电子万年历产业还是存在着较大的问题。

首先,国内电子万年历产业的产业结构严重不合理,相关产业大多数还仅仅停留在劳动密集型产业阶段,使得电子万年历的产量虽大,技术含量却远远不如国外产品[3]。在市场里存在着大量的“垃圾产品”,也严重影响着国产电子万年历的形象。就出现了大量的国内产品严重滞销,而国-外产品销量良好。其次,国内外产品间存在着巨大的技术鸿沟, 技术上的差距也在一定程度上决定了功能以及精度等多方面的差距,这也就造成了国产电子万年历严重缺乏市场竞争力。在市场竞争上的疲软更是让资金无法快速回收,又使得公司缺乏足够的资金去支持技术开发,在产品技术含量的差距上被进一步的拉大,造成严重的恶性循环。

解决这些问题的关键就在于技术革新,加大产品技术上的开发,拓展产品功能,加强精度等各方面的技术要求。本文基于FPGA实现电子万年历,不仅具备基础的计时功能,还加入了温度测量功能,而且在精度上相比于市场上一般的电子万年历也有着明显的优势。

2.FPGA概述

2.1 FPGA简介

FPGA的全称为Field Programmable Gate Array及现场可编程逻辑门阵列,它是在一系列可编程逻辑器件,例如PAL、GAL、CPLD等的研究上演进而来的。作为半定制电路系列产品之一,它的出现既在一定程度上弥补了定制电路,如专用集成电路(ASIC),存在的参数难以调节等不足,又克服了门电路数少这一现在较热门的可编程逻辑器件普遍存在的缺点,受到了相关行业研发工程师的一致好评[4]。

现代IC设计的主流技术就是设计师使用Verilog语言或者VHDL语言这类硬件描述性语言来设计的电路,再通过进行相关布局以及简单综合,再在FPGA芯片上快速调试,来完成相关设计。无论是简单的逻辑门电路电路又或是负责的组合功能电路,都可以使用可编辑元件来实现。而且大多FPGA芯片内,此类可编辑元件也会具备如触发器或者更加完整的记忆块等记忆元件。

设计师们根据所要实现的功能,对相关模块进行连接来完成设计。而当一个FPGA成品出场后,系统设计师还可以在需求改变的时候,去改变FPGA内的逻辑块以及改变逻辑块之间的连接,从而达到可以对不同需求实现不同的逻辑功能的效果[5]。

FPGA的缺点在于相较于专有集成芯片,在速度上有着劣势,也对相对比较复杂的设计束手无策,功耗方面较大也是它存在的问题之一。FPGA的优势在于可以快速成品,价格便宜,可以随时修改程序中所出现的错误,可移植性高。市场上存在着一些价格便宜但是编辑能力有着明显缺陷的FPGA。由于编辑能力的缺陷,无法直接在上面完成设计,一般都是通过在FPGA上进行开发,然后将内容移植到另一芯片上。此外,还可以通过CPLD来进行开发,这也是一种常用手段。

2.2 FPGA工作原理

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三大部分。FPGA作为一种可编辑器件,在结构上与类似GAL、CPLD、PAL器件这类传统的逻辑电路和门阵列完全不同。FPGA实现合并逻辑的方法是是利用16×1RAM的小型查找表去连接D触发器,再由触发器对I/O端口和逻辑电路进行驱动,这种方法实际上就是构成了一个同时能实现将逻辑进行时序化和将逻辑进行组合的基础逻辑单元模块。用金属线将这些模块相连就可以实现所需要的逻辑功能,也可以将这些模块与I/O模块相连接。

FPGA内部有一个静态存储器,里面存储着一些与逻辑相关的数据,FPGA的逻辑功能就可以通过对这些数据的调用。而这些数据又决定了各模块之间(包括与I/O模块之间)的连接方式。也就是说,最终决定了FPGA逻辑能力的是存储器中的数据,它也决定了FPGA的工作能力。而FPGA被人们热烈欢迎的原因也在于它允许使用者进行无限的编程以及它的可移植性,这也就决定了FPGA在优化产品功能有着独一无二的地位。

2.3开发平台Quartus II概述

本文以Quartus II作为开发环境进行设计开发,下面就对Quartus II这款软件进行简单的介绍。

Quartus II可编程逻辑开发软件是Altera公司为其生产的FPGA/CPLD芯片设计的集成化专用开发工具,是Altera最新的一代且功能更强的集成EDA开发软件。Quartus II是一款全面的开发软件,FPGA的整个设计过程都可以用它来完成。

剩余内容已隐藏,请支付后下载全文,论文总字数:32940字

相关图片展示: