论文总字数:41606字

目 录

第1章 绪论 1

第2章 系统方案设计 2

2.1 系统设计框图 2

2.2 总体方案设计分析 3

2.3 数据存储方案设计分析 4

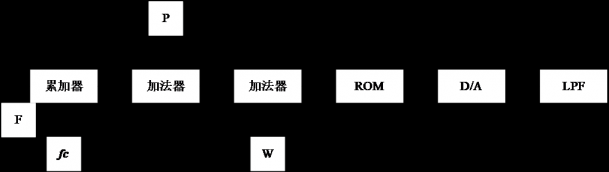

第3章 直接数字频率合成器(DDS)的原理 4

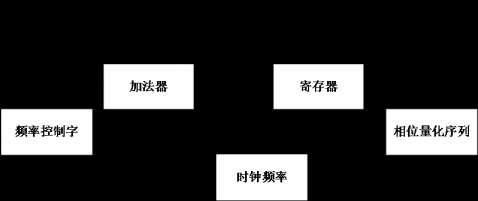

3.1 DDS的原理 4

3.2 DDS的优缺点 6

3.3 DDS的应用 7

第4章 多波形DDS信号源硬件设计 7

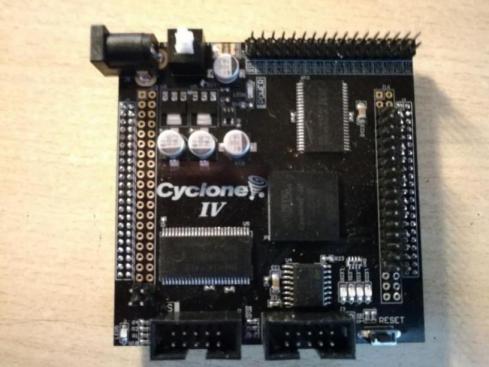

4.1 硬件平台FPGA 7

4.2 DDS模块及内部 8

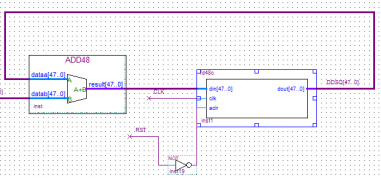

4.2.1 48位相位累加器 8

4.2.2 相位加法器 9

4.2.3 波形存储器 9

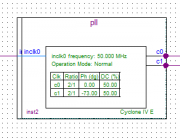

4.3 锁相环模块PLL 9

4.4 Nios Ⅱ软核处理器 10

4.5 D/A转换器和低通滤波器分析 11

4.6 键盘模块设计 13

第5章 多波形DDS信号源软件设计 13

5.1 软件平台Quartus Ⅱ和Nios Ⅱ 14

5.2 硬件描述语言 15

5.3 软核C编程 15

5.3.1 生成波形数据RAM表部分程序 15

5.3.2 键盘控制程序实现 18

第6章 系统功能验证及调试 20

6.1 实验仿真及验证 20

6.2 结果分析与调试 25

6.3 误差分析 25

第7章 总结与展望 26

致谢 27

参考文献 28

附录 29

基于FPGA的DDS多波形信号源设计

孙 江

, China

Abstract: Multi-wave signal generator is widely used in scientific research and teaching experiment. In order to get a variety of waveform whose frequency, amplitude and phase can be adjusted and which have higher precision and better stability,this paper studies the principle of direct frequency synthesizer (DDS) and designs a DDS signal generator based on field programmable gate array (FPGA) . Using Verilog hardware description language to design the underlying module, making use of DDS core module of Quartus Ⅱ, using the RAM to store data, and putting a Nios soft core processor Ⅱ to embed in the FPGA, writing control waveform, frequency, amplitude, phase and square wave duty ratio of the C language program by Nios Ⅱ to control system, which can realize arbitrary waveform real-time output. Experimental results show that in comparison to general signal generator and others which using FPGA signal generator, the method to realize the signal generator can be more flexible to produce a variety of waveform, frequency output range is bigger, adjustable square wave duty ratio and more convenient.

Key words: Multi-waveform signal generator, FPGA, DDS, Nios soft core

第1章 绪论

随着科学技术的不断发展,我们已经迎来信息化高速发展的阶段,电子产品的更新换代促进了信息社会的发展。随着电子设计技术和生产制造技术的空前进步与发展,使得现代的电子产品的集成度和性能的提高以及电子产品更新快速、成本价格降低;前者的核心就是EDA技术。该技术有力地改善了设计效率,让设计者远离了大量具体设计,缩短了研制产品的周期。后者主要是微小件加工,最新已经发展至纳米加工阶段,能够实现集成度更高的芯片。

可编辑逻辑器件在电子技术设计领域的应用早已普及,主要由于可编辑逻辑器件能够通过相应开发软件工具来编程,实现重构器件的硬件结构以及工作方式,这样便使得设计硬件变得像设计软件一样便捷。可编程逻辑门阵列FPGA与单片机或是PC的顺序执行模式不同,主要是并行运算,这样能够实现多任务同时处理,运算能力较强,此外还具有上市时间短,成本低,稳定性好等优点,所以应用广泛。

现场可编程门阵列FPGA是在PAL、GAL、CPLD等可编程的器件的基础上发展而来,作为一种半定制的电路而出现。对于FPGA芯片,不仅结构变得更加简洁合理,运行速度变快,集成度变高以及制作工艺更精益求精,而且开发FPGA的设计方法更加科学,软件开发工具更加方便简洁优化,这一切都得归功于半导体制作加工工艺的快速发展。

微电子技术的空前发展,促使电子设计技术迎来了一个空前发展的时代,主要体现在电子技术以及设备在社会各种行业中的应用以及发展规模。FPGA的巨大市场前景是可见的,FPGA芯片有着集成度高、功耗低、开发周期短暂、开发软件完善、成本低等明显优势,以及制作工艺先进、可嵌入内核处理器等特点,促使FPGA 在市场中份额以及未来可发展性迅速提高。总而言之,对于FPGA的研究与开发是时代所需。

因此,利用FPGA实现多波形DDS信号源的设计,就有了长远的意义,对于今后熟练掌握FPGA打好基础。此外,DDS信号源的设计,也是对我们所学知识的巩固掌握和实际应用,有利于我们今后的发展。

信号发生器最初发明是用于测试接收机,后来上世纪六十年代有了迅速发展,此时仅能产生简单波形,后来随着电子技术的发展,出现各种各样的信号发生器。种类发展多样的同时,这些信号发生器的性能也得到了很大的改善提高,实现功能变多,信号发生器结构变得简易轻便。

上个世纪70年代初,以特尼为代表的研究人员提出了一种从相位出发直接合成波形的频率合成技术——直接数字频率合成器(DDS),不过由于时代技术的局限性以及制作器件工艺水平不高,此种方法实现的信号波形指标不及传统信号发生器产生的波形效果,被当时主流所抛弃。现如今,随着电子技术的飞速发展,DDS技术又重新逐渐得到主流的关注与重视,并取得了迅猛发展。

现如今,信号发生器主要的发展方向有波形发生器的软件开发以及多功能方面,此外,新一代台式仪器形态改变了,具有多种特性。信号发生器的具体发展方向有CPU功能增强,引脚多功能化,内部资源增多,函数信号发生器发展方向。

近些年我国的超大规模集成电路得到越来越多的重视,从而关于DDS的研究和论文发表不绝如缕,不过可惜的是大多数研究的是利用DDS原理改善性能和提高功能,关于DDS芯片的研究则少之又少,使得国内的研究水准较国际水平有着不小的差距。国家近些年重视电子芯片的发展,促进国内芯片产业的发展,将能够推动DDS的深入研究,也涌现一大批芯片研发从业者,也是未来趋势。这就需要我们这一批新鲜血液的输入,促进我国芯片行业的奋起直追。

本设计重点研究DDS技术的原理与应用,基于FPGA实现DDS的功能,利用Verilog硬件描述语言设计底层模块以及Quartus Ⅱ自带的模块构成DDS核,采用RAM存储数据,并将一个Nios Ⅱ软核处理器嵌在FPGA上,通过在Nios Ⅱ编写控制波形、频率、幅度、相位以及方波占空比的C语言程序,控制系统,从而能够实现任意波形实时输出。

第2章 系统方案设计

根据研究内容绘制系统设计框图,对框图各部分剖析,提出各部分设计方案并比较方案的优缺点,结合设计目标,选用最佳方案。

2.1 系统设计框图

2.1.1 系统设计框图

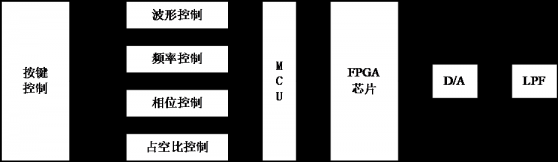

整个DDS系统主要由输入控制模块、MCU、FPGA芯片、D/A模块以及低通滤波器组成,按键控制将波形控制、频率控制、相位控制、占空比传送至MCU,再经FPGA实现DDS功能,最后经D/A模块和低通滤波器输出波形。

2.2 总体方案设计分析

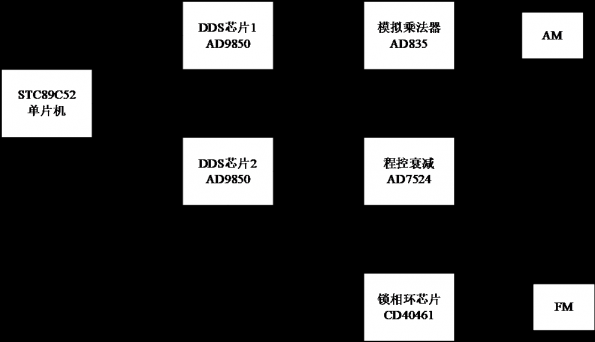

方案一:以STC89C52芯片作为控制芯片,采用美国AD公司的DDS芯片AD9850产生所需波形信号,以及高速DA转换器AD7524实现调幅,系统框图如图2.1.1所示。

2.2.1 系统框图

方案二:利用单片机和FPGA实现直接数字频率合成器 充分利用单片机与FPGA功能的互补性。FPGA与单片机互补工作,FPAG 的作用是根据频率控制字和相位控制字生产对于的波形ROM表,而单片机的作用是传送以上控制字以及控制DA转换器进行幅值转换。就是在加电前每次都要初始化单片机,将写好的程序烧录进系统中,再将键盘输入的频率等数据送至单片机和FPGA,最后经由DA转化器和低通滤波器输出所求波形信号。

方案三:利用Verilog硬件描述语言设计底层模块以及Quartus Ⅱ自带的模块构成DDS核,采用RAM存储数据,并将一个Nios Ⅱ软核处理器嵌在FPGA上,通过在Nios Ⅱ编写控制波形、频率、幅度、相位以及方波占空比的C语言程序,控制系统,再通过高速DA模块,从而实时输出各种波形。

分析:方案一为典型DDS信号发生器设计方案,存在DDS芯片功能过于单一,不符合设计要求和出发点,方案二采用单片机和FPGA结合的方法,不过存在时钟晶振频率低,反应时间长的问题,然而方案三能够完美解决以上问题,并能够实现更多波形,所以成为本设计的选取方案。

2.3 数据存储方案设计分析

方案一:ROM查表法,注意的是,ROM查表的设计会根据具体器件采用不同的方法。例如利用VHDL语句和利用lpm_rom模块生产ROM表,或者利用matlab生成波形采样点的mif文件,作为ROM波形数据表,直接调用并分配地址,然而输入波形复杂或是波形数据大,就比较麻烦。

剩余内容已隐藏,请支付后下载全文,论文总字数:41606字

相关图片展示: