论文总字数:16863字

目 录

1引言 1

1.1频率合成系统发展情况 1

1.2锁相环频率合成技术 1

1.3本文的研究内容 2

2 PLL频率合成电路性能 2

2.1 技术指标 2

2.2.1 锁相环路构成 3

2.2.2环路基本方程 4

2.2.3环路的传递函数 5

2.2.4 环路的稳定性分析 5

2.3本章小结 6

3系统的实现 6

3.1总体设计框图 6

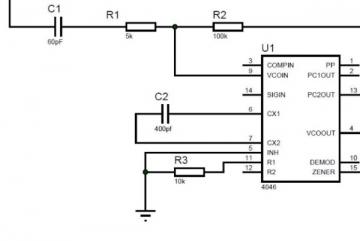

3.2 锁相环CD4046 6

3.3 FPGA的使用 9

3.4 N分频器电路的设计 9

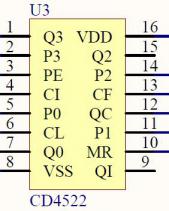

3.4.1 CD4522芯片引脚 10

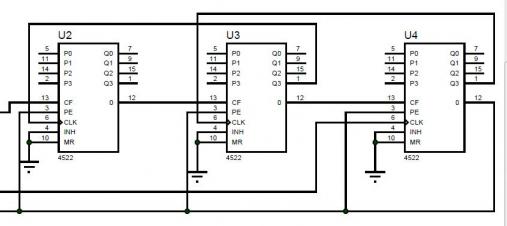

3.4.2 分频电路原理 11

3.5相关外围电路 11

3.6电路工作原理 13

3.7实物的制作 13

3.8本章小结 14

4 系统的仿真与实验 14

4.1 系统的仿真 14

4.2系统的实验 17

4.3数据的误差分析 20

4.4 本章小结 21

5总结 22

参考文献 22

基于PLL技术的程控频率合成器

陆一

, China

Abstract:Frequency synthesis technology has been widely used in various fields such as radio communication systems, control systems, and electronic systems. Frequency synthesizers have become a major component of contemporary electronic communication systems. In this article, a program-controlled frequency synthesizer based on phase-locked loop technology is implemented. FPGA is Used to provide the reference frequency, integrated chip CD4046 for frequency synthesis. The integrated chips CD4522 are cascaded to obtain frequency divider circuit. corresponding peripheral circuits are designed, then the whole frequency synthesis circuit is realized. The scheme and principle of system design are elaborated, and the functions of each involved chip are analyzed in detail. The feasibility and effectiveness of the system are verified through simulation and experiments. The measurement and error analysis of the physical object are done, the results show that the design can realize the output of 1kHz. Signal frequency to 999kHz. The designed frequency synthesis can be used as frequency source, frequency meter or teaching experiment.

Keywords : Phase-locked loop technology ; CD4046 ; frequency synthesis; program-controlled

1引言

在现代通信系统中,频率合成技术一直是其重要的组成部分之一,究其本质,它就是利用四则运算,把一个高度稳定和高度精确的基准频率变为用户所需的精确的、稳定的任意频率。频率合成器被广泛的应用在各类仪器仪表、电子系统、通信雷达等方面,有着重要的地位和作用。本文将使用FPGA芯片、集成锁相环芯片、分频计数芯片相结合,设计出一个频率合成器,使其能够生成任意的1kHz至999kHz的任意整数频率。具有一定的使用价值。

1.1频率合成系统发展情况

频率合成(Frequency Synthesis)技术目前在无线电通信系统、控制系统和电子系统等各个领域中均得到普遍使用。频率合成器已经成为当代电子通讯体系的主要组成部分,被广泛应用在各类仪器仪表、通信雷达、电子系统中。

频率合成,顾名思义就是能够在输出端获得所需要的特定频率的信号,要实现这样的信号,额外需要在输入端提供一个用来“参考”的信号,也就是对它进行运算合成工作。频率合成器于是就基于这个道理从而设计出来的频率源。现如今,频率合成技术通过自身的不断发展已经日趋成熟,目前可供参考的频率合成方式总体来看有四种主要的方式:间接合成、直接合成、混合式合成和直接数字合成。在进行频率合成时,当他的高频谱纯度越高、相位噪声越低、输出频段越高、步进跳变越小、跳变速度越快,则表明该频率合成器的质量越好[1]。

自上个世纪30年代以来,直接频率合成技术出现,它的原理就是用一个晶振源,通过信号变换,产生出所需要的频率的信号,通过这种方案获得信号稳定度在长期和短期来看都很高、同时频率变换速度也快。其瑕疵就是结构复杂,成本较高,需要运用许多的器件对信号进行处理。正是因为上述的问题存在,直接频率合成技术被单独使用的机会不多。

到了上个世纪60年代末期,诞生了锁相环式的间接频率合成技术,它所具备的好处就是输出的频谱比较集中不易杂散、输出的频率范围更宽、输出频率能够很好地得到控制。然而,他的短板就是难以实现跳频、频率转换时间相对其他方案较长。只能通过牺牲输出频谱的相位噪声指标来换取小的步进,同时也难以获得高分辨率输出频率质量。从技术上看,利用锁相环进行的频率合成方式总共由环路滤波器、鉴相器 、压控振荡器和分频器构成[2]。

1.2锁相环频率合成技术

目前主流的频率合成器一共分为四种方式[3],分别是:锁相式、直接式、直接数字式和混合式。锁相式频率合成方法能够轻易的缩小体积,便于模块化的移植,可以进行工程化,随着技术的发展,它所具备的性能也越来越好,所以这两种方式正在成为频率合成器制作和普遍使用的典范。本文将采用锁相式频率合成的方式,选取集成芯片CD4046作为核心器件,设计相应的外围电路,选取FPGA芯片提供所需的基准频率进行系统的实现

对于锁相式频率合成器的原理进行分析,其实就是对信号的相位和频率进行跟踪,再反馈到输出端。当进行工作时,环路的作用时提供稳定的频率,并且对于基准信号进行加减乘除的运算。可以用一阶微分方程来表示和分析它的系统特性。它的基本构成如下图1.1所示[4]。

图1.1 锁相环基本构成图

图1.2的可以描述为:当电流通过鉴相器到达低通滤波器的时候,电流的平均直流值乘以低通滤波器的阻抗就形成了控制压控振荡器的控制电压[5]。控制电压会作用于压控振荡器,并且对压控振荡器的输出相位进行调整,直到两者之间的相位差为0。N分频器在图中的功能是对压控振荡器的输出信号进行分频,然后与分频后的原始基准频率进行比较,并利用产生的误差来控制电压,并再来控制压控振荡器的相位。因此,比较频率相位就等于压控振荡器的输出除以N。可以用公式表示为:

1.1)

1.1)

在现实应用中N值是可以自行设置的,R和XTAL共同确定输入的基准频率[6]。该式只有在锁相环入锁状态的期间才成立。

1.3本文的研究内容

根据对数字频率合成技术原理分析和使用情况,本文将对以下5点内容进行详细论述:

1、简要概括频率合成技术的发展现况,具体阐述锁相环频率合成相关性能指标并进行分析。

2、阐述了FPGA产生1kHz基准频率原理与PLL芯片CD4046的工作原理。

3、介绍系统的硬件信息,对涉及的芯片如何使用进行说明,详细解释频率合成的硬件设计以及工作原理。

4、对最终的设计系统进行软件仿真。

5、对全文进行总结。

2 PLL频率合成电路性能

2.1 技术指标

为了方便了解、设计和使用基于锁相环的频率合成器,需要对它提出各种涉及的技术质量指标[7]。在不同的电子系统或者通信系统中使用到PLL频率合成时,对于它提出的要求也不一样。笼统的讲,一个频率合成器需要涉及诸如频率合成范围、频率合成间隔、频率精确度稳定度以及频率转换时间等相关指标,这些指标的不同会影响到器件的成本、体积以及功耗的因素。因此需要提出一些技术指标的概念[8],在分析的时候可以定性的了解它的性能。

2.2锁相环路工作原理及性能分析

2.2.1 锁相环路构成

1 鉴相器(PD)

鉴相器[9]在环路中是用来比较输入到鉴相器的两种信号的相位的。简言之,鉴相器在系统中的作用是将相位差转换成电压[10]。理想相位检测器输出电压Vd的平均分量与输入信号的相位差成正比:

(2.1)

(2.1)

在这个公式中, Ad是相位敏感的,它的单位是V/rad。当相位为正弦时,输出电压Vd(t)和误差相位由以下表达式表示:

(2.2)

(2.2)

剩余内容已隐藏,请支付后下载全文,论文总字数:16863字

相关图片展示: