论文总字数:29715字

摘 要

现代通信技术发展迅速,在高速率的信息传输系统中,均衡技术逐渐成为不可或缺的一部分。而均衡技术中,最大似然检测电路因性能优越备受关注。

本文设计了应用于部分响应系统的最大似然序列检测(PRMLSD)均衡器,该均衡器由Viterbi算法实现,并用Matlab与Modelsim对均衡器做了联合仿真。文中首先介绍了码间干扰与主要的常用均衡技术及其算法。其次重点探讨了最大似然检测电路的常用算法Viterbi算法,并对如何实现Viterbi译码器做了详细分析。之后,搭建了Matlab与Modelsim联合仿真平台,利用Matlab描述ADC量化模块,HDL编写Viterbi 译码器电路来实现均衡。最后对基于Viterbi算法的PRMLSD均衡器进行了性能仿真,给出误码率曲线,并作了简要分析。结果表明,对于给定的部分响应系统,在加性高斯白噪声条件下,输入信噪比越高,误码率越低。对于相同的输入信噪比,信道的插入损耗越高,误码率越高。

关键词:最大似然序列检测,Viterbi,均衡,判决反馈均衡

Design of Maximum Likelihood Sequence Detection (MLSD) for Partial Response System

Abstract

With the development of modern communication technology, equalization technology has become an integral part of high-speed information transmission system. In the equalization technology, maximum likelihood sequence detection is given more attention because of its superior performance of the circuit.

In this paper, the maximum likelihood sequence detection equalizer for partial response system is designed, and the equalizer is realized by Viterbi algorithm. The equalization is simulated using Matlab combined with Modelsim. At first, the inter symbol interference and the main common equalization techniques and their algorithms are introduced. Secondly, the Viterbi algorithm of the maximum likelihood detection circuit is discussed, and the Viterbi decoder is analyzed in detail. After that, the Matlab and Modelsim co-simulation platform is built, and the ADC quantization module is described by Matlab. The part of the decoder is written in Modelsim, and the Viterbi decoder is used to equalize the target signal. Finally, the performance of the Viterbi decoder is simulated, and the error rate curve is given and briefly analyzed. The results show that for the given partial response system, the higher the input SNR is, the lower the bit error rate is. For the same input SNR, the higher insertion loss of the channel is, the higher bit error rate is. At the end of the paper, the pre simulation report and a logic synthesis circuit diagram of the selected unit are also attached.

KEY WORDS: maximum likelihood sequence detection, Viterbi, equalization, decision feedback equalization

目录

第一章 绪论 1

1.1 引言 1

1.2研究意义 2

1.3本文主要研究内容 3

第二章 码间干扰及均衡 4

2.1 码间干扰 4

2.2 均衡技术 4

2.2.1 均衡的分类 4

2.3.2 离散时间线性均衡 5

2.3.3 判决反馈均衡[13][14] 8

2.4 本章小结 11

第三章 最大似然序列检测(MLSD)原理及算法 12

3.1 部分响应系统 12

3.2 最大似然序列检测(MLSD)原理 12

3.2 维特比算法原理[4] 14

3.2.1 卷积码 14

3.2.2 维特比算法 16

3.2.3 基于Viterbi算法的最大似然序列检测(MLSD)均衡器 18

3.3 本章小结 24

第四章 PRMLSD的仿真及综合 25

4.1 系统仿真 25

4.2 仿真方案 25

4.2.1 基于Matlab的ADC仿真 25

4.2.2 基于Viterbi算法的PRMLSD均衡器仿真 26

4.3 仿真结果 29

4.3.1 Viterbi译码器的性能仿真 29

4.3.2 Viterbi算法电路的综合 33

(1) Design Compiler综合结果 33

(2) 综合后的电路图 37

4.4 本章小结 37

第五章 总结 38

致谢 39

参考文献(References) 40

第一章 绪论

1.1 引言

现代通信系统发展迅速,在人类的生活中已变得不可或缺。生活中需要用到通信系统的例子有很多,很多情况要求现代通信系统有更高的传输速率,并且具有更高的可靠性。

在高速通信以及无线通信领域,信道对信号的畸变将更加的严重,加上多径传输、信道衰落等影响,在接收端接收到的信号会产生严重的码间干扰(Inter-Symbol Interference),从而使得按照以往的编码译码系统进行通信的系统产生较高误码率。一旦误码率变高,在实际工程中是不具备应用价值的。其次,一个信号包含很多频率分量,信道衰落对于不同频率的信号衰减幅度是不一样的,往往高频率的信号比低频率的信号衰减幅度更大,此时也会产生码间干扰。再者,不同的频率分量的传播速度也是不一样的,频率越高的传播速度相对越快,这也是产生码间干扰的一部分原因。

码间干扰的产生会影响整个通信系统的性能,要消除码间干扰,需要在接收端对接收信号进行处理再送送入译码,或发射端对发送信号进行处理再发送,这便是均衡技术。均衡是针对信道特性而言的,对一个信号的均衡的目的是消除由于信道特性而引起的码间干扰,即借助均衡对信号做出与信道特性相反的处理或预处理,用来减小或消除由于信道的不理想特性导致的码间干扰。自适应均衡能够通过已接收到的信号自动不断地调节系数从而跟踪信道。换句话说,信道的特性可以通过滤波器的系数参数来表示或代入。通常均衡技术的一项关键问题在于如何通过信号确定该信号所经过信道的信道特性,以便对已受干扰的接收信号进行反处理。

均衡技术中最新的技术为最大似然序列检测[11]。最大似然序列检测与其他均衡技术在原理上有着本质的区别,因而仿真效果一直是最好的。线性均衡以及反馈判决均衡器对接收信号进行自适应滤波,并通过滤波所得信息与接收信号相加,从而将码间干扰降低。最大似然序列检测均衡器属于非线性均衡技术的范畴,与线性均衡以及判决反馈均衡器不一样,最大似然序列检测均衡器本质上是利用信道特性计算出所发送码字经过信道后所有可能的接收码字,并将实际接收序列与其对比,找出与接收序列最为接近的计算得出的序列,并将此序列对应的发送码字输出作为均衡结果。由于通常的均衡技术的结果取决于信道特性是否估算正确,而最大似然序列检测是通过序列中码元间的相关性得出最有可能是发送码字一组估计码字,这种均衡机制可以与信道参数估计结合,从两个方面降低或消除码间干扰。因而,最大似然序列检测均衡器被认为是性能最佳的均衡器[12]。

1.2研究意义

实际通信系统中的信道具有不理想特性,比如多径衰落,码间串扰等会导致信道传输能力低下。克服多径衰落主要采用多集技术,而克服码间串扰就需要用到均衡技术。典型的通信系统系统往往由发射器,信道及接收器组成。发射器通常由编码器,调制器组成,可能还包含复杂的锁相环电路,预加重电路等。而接收器可能内置可变增益放大器,CDR时钟恢复电路,现行均衡电路,反馈判决均衡电路等等。若码间串扰严重,则解调器解调后的信号在译码器中译码时很难正确译码,这时候就需要均衡器,在接收信号进入译码器之前经过均衡器将信号间的码间串扰消除或减弱,所以均衡器的好坏常常会影响到最后的译码器的误码率。不管哪种方法,都需要正确得知信道参数,从而将信号经过信道时代入的码间串扰消除。很多情况下,并不是译码器译码产生了错误,而是进入译码器的信号本身就含有过多的码间串扰。

在Ghz以上长距离高速串行互连中,仅仅做好通道的优化远远不够,还需要调整预加重和均衡参数才能实现数据的可靠传输。

在部分响应系统中,常常可以利用部分响应系统的特性对码间串扰加以利用,从而提高信道传输能力。因为码间串扰可以被均衡器消除,信道传输能力得以被提高,从而在相同时间内发送更多的码字,提高信息传输速率。

假设一个部分响应系统的冲击响应如图所示为h(t)=0.4δ(t) 0.2δ(t-1) 0.1δ(t-2)。假设发送端发送码字m=[1 1 0 0 1 0 1 0],则接收端收到的模拟信号对应为u=[0.4 0.6 0.3 0.1 0.4 0.2 0.5 0.2],这一串模拟信号显然直接送入译码器是不能够正确译码的,所以若没有均衡器,发送端每发送一个码元,则需等待冲击响应的大致周期T,从而避免后一个码元受前一个码元的码间串扰影响。若此时,模拟信号进入译码器前经均衡器均衡,可得到信号m=[0.4 0.4 0 0 0.4 0 0.4 0],再送入译码器,则不会产生误码。因为均衡器的存在使得部分相应系统的信息传输频带的利用率得以提高。

1.3本文主要研究内容

主要研究内容为最大似然序列检测均衡器的设计、仿真及综合。本文采用数字电路设计方法,首先采用Matlab进行系统仿真,然后用Verilog HDL进行电路设计并进行前仿真,最后采用综合工具Design Compiler对设计的电路进行综合。

第二章 码间干扰及均衡

2.1 码间干扰

码间干扰可以由两方面原因引起:(1)有时信道对于信号的不同频率的衰减是不一样的,一般频率越高衰减越大;(2)不同频率的信号传播速度也不相同,频率越高,传播速度越快。

不同频率的衰减不一会导致信号边沿变缓,因而单个脉冲的响应展宽,脉冲响应的“拖尾”延伸到下一个bit位,叠加在下一个脉冲的响应上就会改变下一个脉冲响应的幅度。

因而,衰减引起码间干扰的根本原因并非“衰减”本身,而是信道“衰减的频率相关特性”。如果信道的衰减特性对于信号中所有的频率分量都是一样的,就算衰减量很大,也只会引起信号整体幅度的减弱,并不会改变信号的边沿形状。

信号的不同频率成分传播速度不同,信号到达接收端时,会发生“色散”,这也会导致响应的展宽。不同频率的信号传播速度不相同,会使得信号到达接收端时的相位的相对关系发生变化。而这种相对的相位关系发生变化会导致各个频率成分非相干叠加,造成波形的展宽和幅度变化,因此也会导致码间干扰。

2.2 均衡技术[19]

2.2.1 均衡的分类

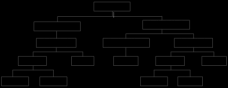

按所在位置可分为:发送端均衡(预加重、去加重)、接收端均衡。按实现原理可分为:线性均衡、非线性均衡(最常见的事反馈判决均衡,简称DFE)。线性均衡又可进一步分为:连续时间均衡,简称CTLE(包括无源CTLE和有源CTLE两种)、离散时间线性均衡(DLE)。离散时间线性均衡(DLE)一般使用FIR滤波器实现,由于没有反馈电路,只有前馈部分,因此工程中常称为FFE(Feed Forward Equalizer)。发送端均衡(预加重及去加重)通常用CTLE或FFE实现,而接收端均衡可以用CTLE、FFE、DFE实现。图2.1列出了在高速串行电路中常见的预加重和均衡方法。

图2.1 均衡分类

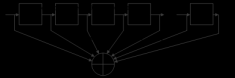

2.3.2 离散时间线性均衡

若传输的信号是数字信号,那么改变信号的频谱特征也可以采用数字滤波器来实现。离散线性均衡的原理就是利用数字滤波器来实现对信号的高通滤波,通常采用FIR滤波器的形式来实现,通过调整FIR滤波器各个抽头的系数来改变滤波器的频响特性。图2.2是这种离散线性均衡的原理框图,由于没有反馈环路,工程上这种均衡器常被称为FFE(Feed Forward Equalizer)。

剩余内容已隐藏,请支付后下载全文,论文总字数:29715字

相关图片展示:

该课题毕业论文、开题报告、外文翻译、程序设计、图纸设计等资料可联系客服协助查找;